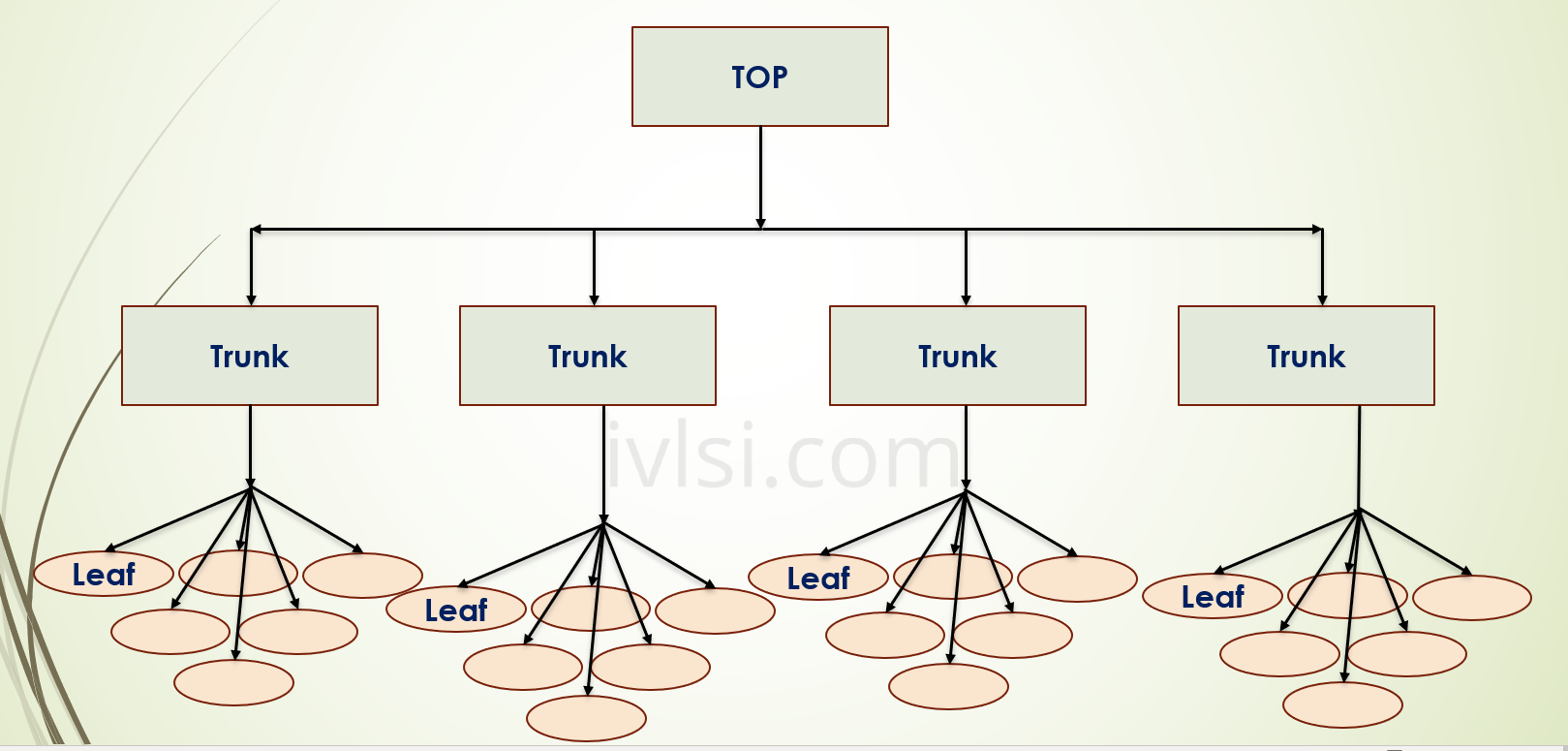

Fishbone Clock Tree . Clock tree synthesis starts the process of signal routing considering the most time critical signals. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the cells using clock inverters and clock buffers. The aim is to distribute the clock signal to all.

from ivlsi.com

Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the cells using clock inverters and clock buffers. Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is to distribute the clock signal to all.

Clock Tree Synthesis in VLSI Physical Design

Fishbone Clock Tree Clock tree synthesis starts the process of signal routing considering the most time critical signals. Clock tree synthesis starts the process of signal routing considering the most time critical signals. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the cells using clock inverters and clock buffers. The aim is to distribute the clock signal to all.

From vlsi.kr

Clock Tree Synthesis(CTS)의 기본 알고리즘, HTree, Fishbone, Mesh, Low Power CTS Fishbone Clock Tree Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is to distribute the clock signal to all. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From www.youtube.com

Lecture on Clock Tree Synthesis Physical Design flow YouTube Fishbone Clock Tree Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is to distribute the clock signal to all. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From ivlsi.com

Clock Tree Synthesis in VLSI Physical Design Fishbone Clock Tree Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the cells using clock inverters and clock buffers. The aim is to distribute the clock signal to all. Clock tree synthesis starts the process of signal. Fishbone Clock Tree.

From www.slideserve.com

PPT VLSI Physical Design Automation PowerPoint Presentation, free Fishbone Clock Tree Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is to distribute the clock signal to all. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From www.analogictips.com

Clock Tree 101 Fishbone Clock Tree Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is to distribute the clock signal to all. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From vorasaumil.wixsite.com

Clock Tree Synthesis Part 3 Clock Structures, its Implementation Fishbone Clock Tree The aim is to distribute the clock signal to all. Clock tree synthesis starts the process of signal routing considering the most time critical signals. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From www.concept.de

RTLvision PRO Fishbone Clock Tree Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is to distribute the clock signal to all. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From www.semanticscholar.org

Figure 12 from The ConicalFishbone Clock Tree A ClockDistribution Fishbone Clock Tree Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the cells using clock inverters and clock buffers. Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is. Fishbone Clock Tree.

From vlsi.kr

Clock Tree Synthesis(CTS)의 기본 알고리즘, HTree, Fishbone, Mesh, Low Power CTS Fishbone Clock Tree Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is to distribute the clock signal to all. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From vlsibegin.blogspot.com

CTS Clock Tree Synthesis Fishbone Clock Tree Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is to distribute the clock signal to all. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID830138 Fishbone Clock Tree The aim is to distribute the clock signal to all. Clock tree synthesis starts the process of signal routing considering the most time critical signals. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Fishbone Clock Tree Clock tree synthesis starts the process of signal routing considering the most time critical signals. The aim is to distribute the clock signal to all. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From www.semanticscholar.org

The ConicalFishbone Clock Tree A ClockDistribution Network for a Fishbone Clock Tree Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the cells using clock inverters and clock buffers. The aim is to distribute the clock signal to all. Clock tree synthesis starts the process of signal. Fishbone Clock Tree.

From ivlsi.com

Clock Tree Synthesis in VLSI Physical Design Fishbone Clock Tree The aim is to distribute the clock signal to all. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the cells using clock inverters and clock buffers. Clock tree synthesis starts the process of signal. Fishbone Clock Tree.

From eureka.patsnap.com

Method for extracting clock tree based on comprehensive netlist in chip Fishbone Clock Tree The aim is to distribute the clock signal to all. Clock tree synthesis starts the process of signal routing considering the most time critical signals. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.

From www.semanticscholar.org

Figure 12 from The ConicalFishbone Clock Tree A ClockDistribution Fishbone Clock Tree Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the cells using clock inverters and clock buffers. The aim is to distribute the clock signal to all. Clock tree synthesis starts the process of signal. Fishbone Clock Tree.

From www.youtube.com

Mesh based clock distribution YouTube Fishbone Clock Tree Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the cells using clock inverters and clock buffers. The aim is to distribute the clock signal to all. Clock tree synthesis starts the process of signal. Fishbone Clock Tree.

From www.researchgate.net

Graphic representation of the clock tree structure Download Fishbone Clock Tree The aim is to distribute the clock signal to all. Clock tree synthesis starts the process of signal routing considering the most time critical signals. Cts (clock tree synthesis) is the process of connecting the clock from clock port to the clock pin of sequential cells in the design by maintaining minimum insertion delay and balancing the skew between the. Fishbone Clock Tree.